13th European Conference on Applied Superconductivity, Geneva, 17-21 September 2017

# Recent research developments of adiabatic quantum-flux-parametron circuits technology toward energy-efficient high-performance computing

N. Yoshikawa<sup>1,2</sup>, N. Takeuchi<sup>2</sup>, C.L. Ayala<sup>2</sup>, Q. Xu<sup>2</sup>, K. Fang<sup>1</sup>, N. Tsuji<sup>1</sup>, F. China<sup>1</sup>, Y. Murai<sup>1</sup>, T. Ortlepp<sup>2,3</sup>, Y. Yamanashi<sup>1,2</sup>

<sup>1</sup>Department of Electrical and Computer Engineering, Yokohama National University, Japan <sup>2</sup>Institute of Advanced Sciences, Yokohama National University, Japan <sup>3</sup>The CiS Research Institute for Microsensor Systems GmbH, Germany

### **Outline**

- Background and motivation

- Operation principle of adiabatic quantum flux parametron (AQFP)

- AQFP as an energy-efficient logic circuit

- Evaluation of AQFP as a logic circuit

- Design methodology of AQFP logic circuits

- EDA tools for Top-Down design

- Summary

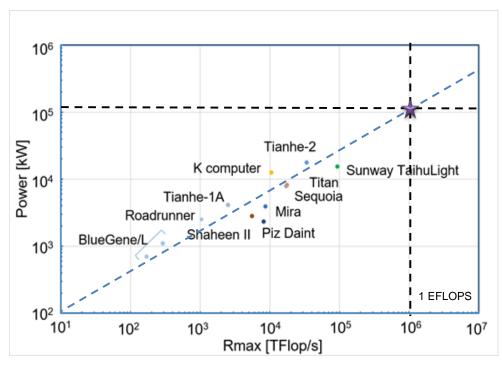

# **Background**

Estimated power consumption to realize an exa-scale computer

- > 100 MW

- ~ \$million/100 MW per year

#### K computer (Japan)

Peak performance: 10.5 PFLOPS Power consumption: 12.6 MW

#### 1st-ranked computers in recent TOP500

http://www.top500.org/

Low-Power Logic Devices is highly demanded.

# **Energy-Efficient SFQ Circuits**

#### **DC Powered**

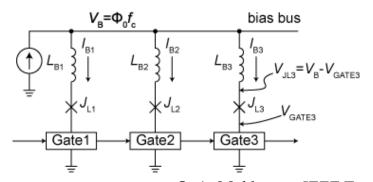

#### **ERSFQ** (Hypres)

$P_{\rm S} \sim P_{\rm D} \sim I_{\rm c} \Phi_0 f$

O. A. Mukhanov, *IEEE Trans. Appl. Supercond.* **21**, 760 (2011).

# LV-SFQ (Nagoya Univ.)

#### **AC Powered**

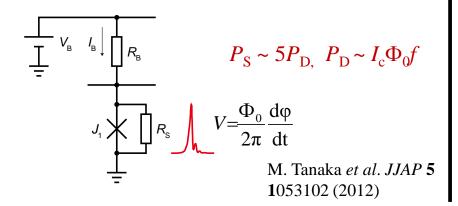

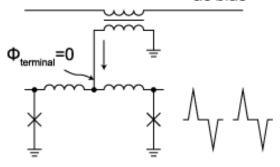

#### **RQL (Northrop Grumman)**

ac bias

$P_{\rm S} \sim 0$ ,  $P_{\rm D} \sim I_{\rm c} \Phi_0 f$

Q. P. Herr *et al.*, *J. Appl. Phys.* **109**, 103903 (2011).

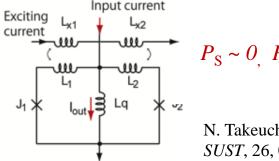

#### **AQFP (Yokohama National Univ.)**

$P_{\rm S} \sim \theta$ ,  $P_{\rm D} < I_{\rm c} \Phi_0 f$

N. Takeuchi, *et. al.*, *SUST*, 26, 035010 (2013).

YNU YOKOHAMA National University

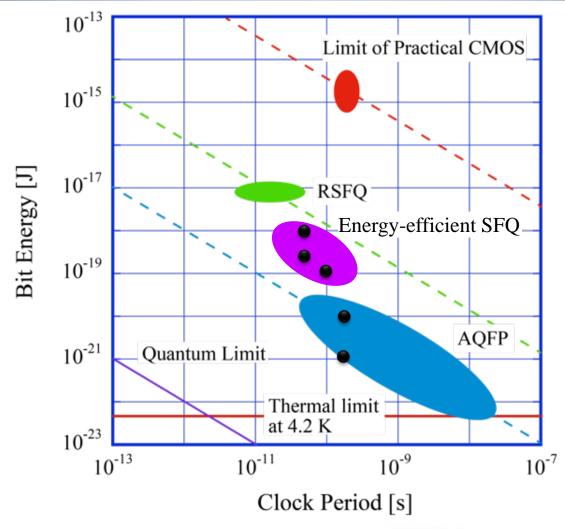

# **Comparison of Energy-Delay Product**

# Adiabatic Quantum-Flux-Parametron (AQFP)

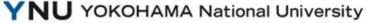

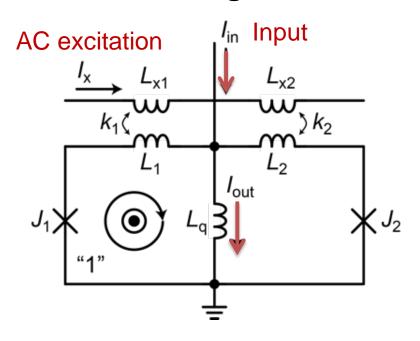

#### **AQFP** gate

An SFQ is stored in the right or left loop depending on  $I_{in}$ .

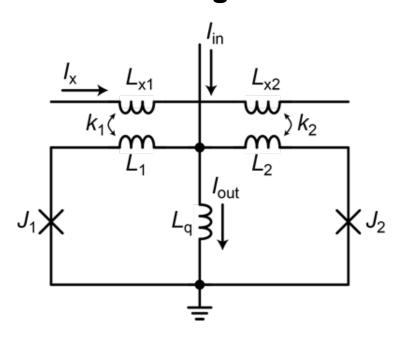

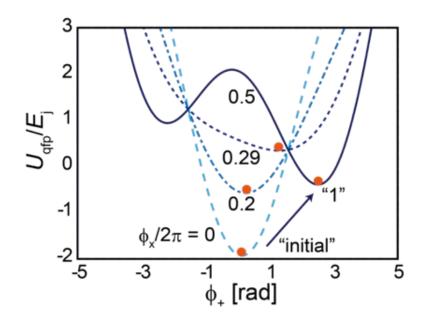

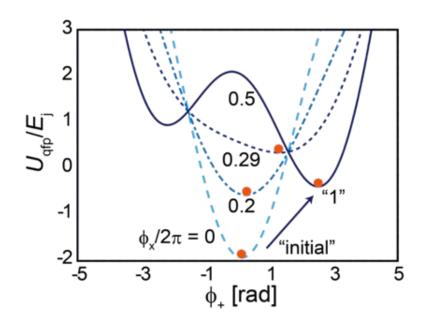

#### Potential energy of the gate

Potential energy changes adiabatically during switching.

Operation principle is based on QFP gates.

# Adiabatic Quantum-Flux-Parametron (AQFP)

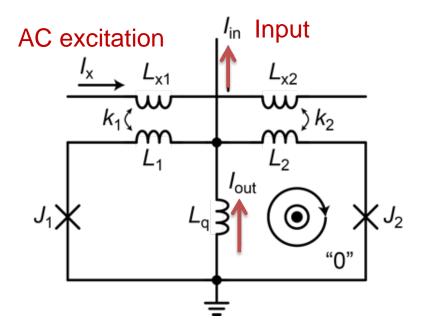

#### **AQFP** gate

I<sub>out</sub> flows downward.

#### Potential energy of the gate

Potential energy changes adiabatically during switching.

Operation principle is based on QFP gates.

# Adiabatic Quantum-Flux-Parametron (AQFP)

#### **AQFP** gate

*I*<sub>out</sub> flows upward.

#### Potential energy of the gate

Potential energy changes adiabatically during switching.

Operation principle is based on QFP gates.

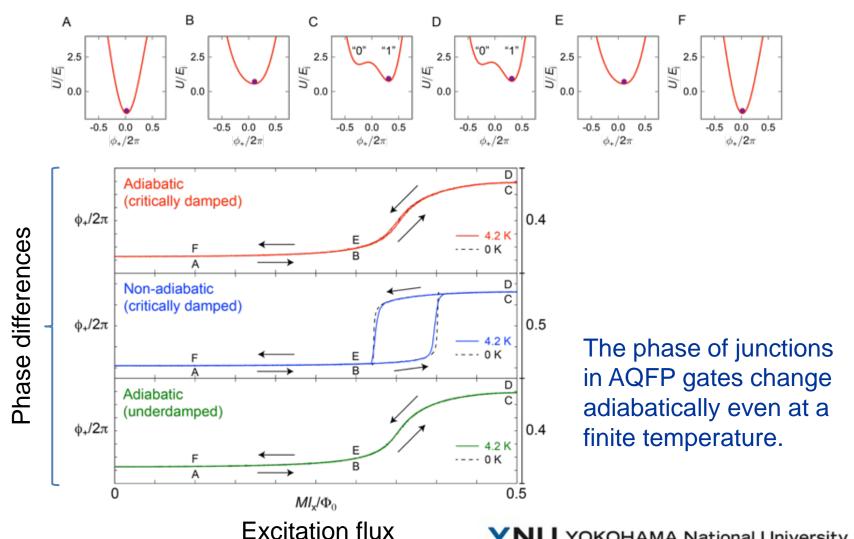

### **Evolution of Junction Phase at 4.2 K**

YNU YOKOHAMA National University

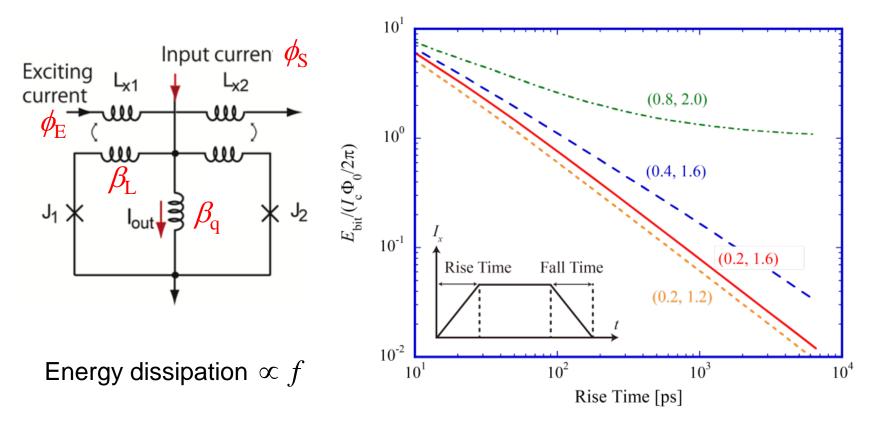

### Bit Energy vs. Clock Period of AQFP

When rise time is 1000 ps,  $E_{\rm bit} = 0.023 \, I_{\rm c} \Phi_0$  (~  $20 k_{\rm B} T$ ).

→ 1/1000 of RSFQ

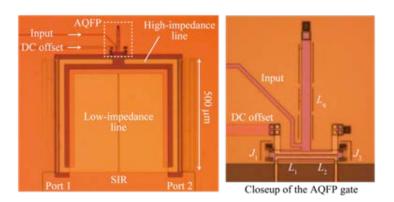

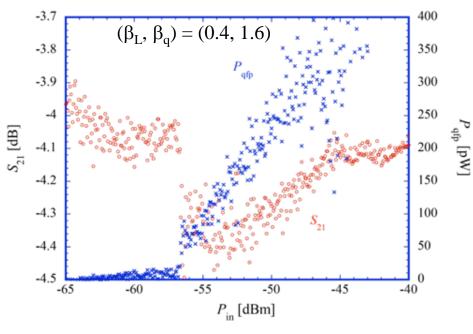

# Bit Energy Measurement of AQFP using a Superconducting Resonator

# Measurement System | Weak | High Q | AQFP | AQFP |

Clock frequency: 4.998 GHz

Q of resonator: 357

#### Measured power consumption of AQFP

$$P_{\rm qfp} \sim 50 \text{ pW}$$

$E_{\rm bit} \sim 10 \text{ zJ} \sim 170 k_{\rm B}T$

AIST Nb Josephson standard process (STP2) was used.

# Comparison of Superconducting Logics

| Logic         | Clock Freq.<br>[GHz] | $E_{bit}/I_{c}\Phi_{0}$ | Typical I <sub>c</sub><br>[μΑ] | EDP<br>[aJ·ps]         |

|---------------|----------------------|-------------------------|--------------------------------|------------------------|

| CMOS          | 4                    | -                       | -                              | ~10 <sup>5</sup>       |

| RSFQ [1]      | 50                   | 19                      | 150                            | 120                    |

| eSFQ [2]      | 20                   | 0.8                     | 150                            | 12                     |

| RQL [3]       | 10                   | 0.33                    | 150                            | 10                     |

| LV-RSFQ [4]   | 20                   | 3.5                     | 150                            | 54                     |

| AQFP [5]      | 5                    | 0.0042                  | 50                             | 0.086                  |

| Quantum limit | -                    | -                       | -                              | 5.3 × 10 <sup>-5</sup> |

- [1] X. Peng et al., IEICE Trans. Electron. **E97.C**, 188 (2014).

- [2] M. H. Volkmann et al., Supercond. Sci. Technol. **26**, 015002 (2013).

- [3] Q. P. Herr et al., J. Appl. Phys. **109**, 103903 (2011).

- [4] M. Tanaka et al., IEEE Trans. Appl. Supercond. 23, 1701104 (2013).

- [5] N. Takeuchi et al., Supercond. Sci. Technol. 28, 015003 (2015).

# **Evaluation of AQFP as a Logic Circuit**

# Important metrics as a logic circuit

- Gain

- Functionality

- Speed

- Energy consumption

- Driving ability

- Connectability

- Error rates

- Robustness

- Density

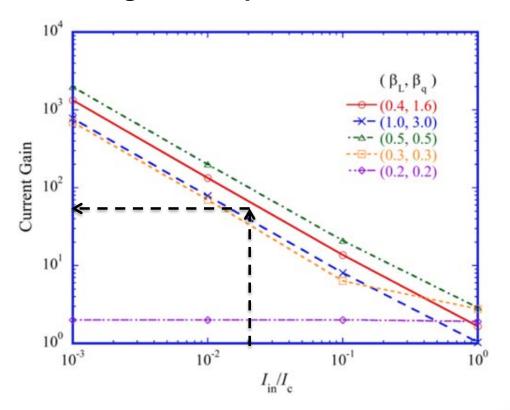

### Gain

Current gain of AQFP is considerably large.

#### Current gain vs. input current at T = 0K

If we assume

$\delta I_{in} \sim 1 \ \mu A$ , and  $I_c = 50 \ \mu A$ , the current gain is given by  $I_c / \delta I_{in} \sim 50$ .

$\delta I_{in}$ : input thermal noise

cf. In RSFQ circuits with  $I_{in} \sim 20~\mu\text{A},~I_{c} = 100~\mu\text{A},$  the current gain is  $\sim 5$ .

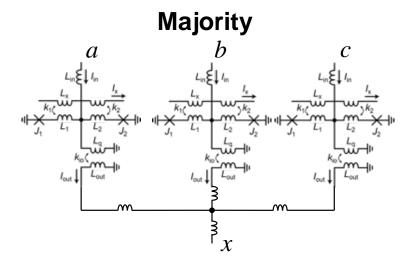

# **Functionality**

- NOT gate is cost free.

- Majority gate is a basic logic gate.

NOT gate is made by using a transformer with negative coupling.

Buffer NOT  $L_{in} \not = l_{in} \qquad l_{in}$

Majority gate is made by connecting three buffers in parallel.

$$x = MAJ(a, b, c) = ab + bc + ac$$

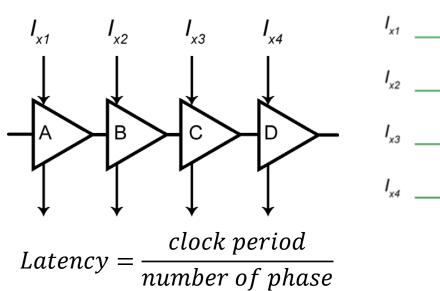

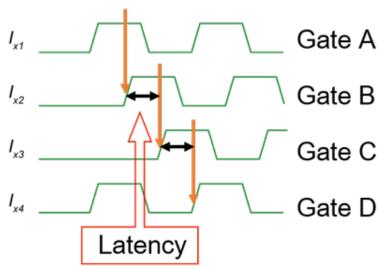

# **Speed**

- AQFP is driven by multi-phase clocks. (4-phase is typically used.)

- Target clock frequency is 5 GHz.

- Double excitation method can increases the clock frequency [1].

- Latency is improved by increasing the number of phase.

#### **Clocking of AQFP gates**

# **Energy Consumption**

- The static energy consumption is zero, the dynamic energy consumption is proportional to the clock frequency.

- The energy consumption is decreased by using high- $J_c$  and high- $\beta_c$  junctions.

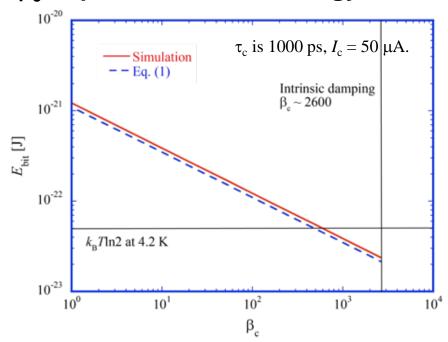

#### $\beta_c$ Dependence of Bit-Energy of AQFP

Bit energy:

$$E_{bit} = 2I_c \Phi_0 \frac{\tau_{sw}}{\tau_{rf}}$$

Intrinsic switching time:

$$\tau_{sw} \approx \frac{\Phi_0}{I_c R} = \sqrt{\frac{2\pi\Phi_0 c}{\beta_c j_c}}$$

# **Driving Ability**

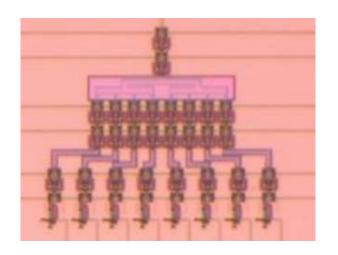

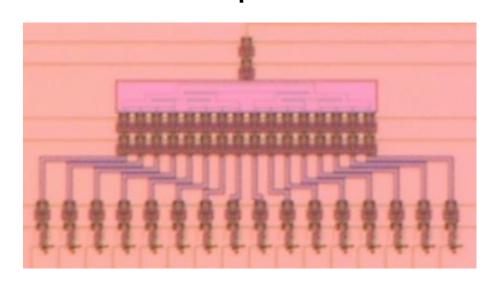

■ Fan-out of AQFP gate is large (4 ~ 16).

1:8 splitter

1:16 splitter

(cf. Fan-out of RSFQ circuits: 2 ~ 3.)

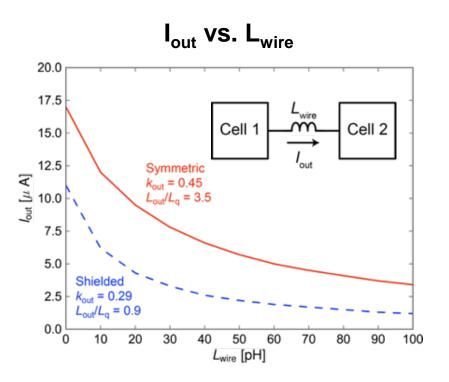

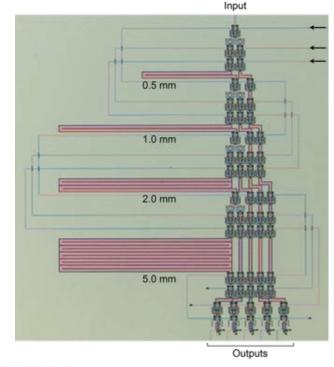

# Connectability

- The output current of AQFP gate decreases with increase of interconnect inductance, which limits the wire length.

- $\blacksquare \ \mathsf{L}_{\mathsf{max}} \sim 1 \ \mathsf{mm}.$

#### Testing of maximum wiring length

N. Takeuchi et al., J. Appl. Phys. 117, 173912 (2015). YNU YOKOHAMA National University

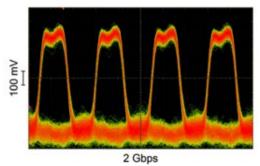

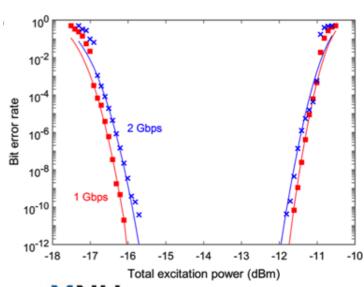

### **Error Rates**

■ Bit-error-rate of AQFP gate is quite small when  $E_J >> k_BT$ .

#### 2 GHz bit-error-rate test results

YNU YOKOHAMA National University

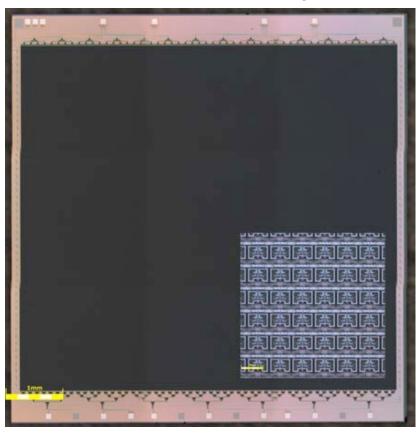

#### Robustness

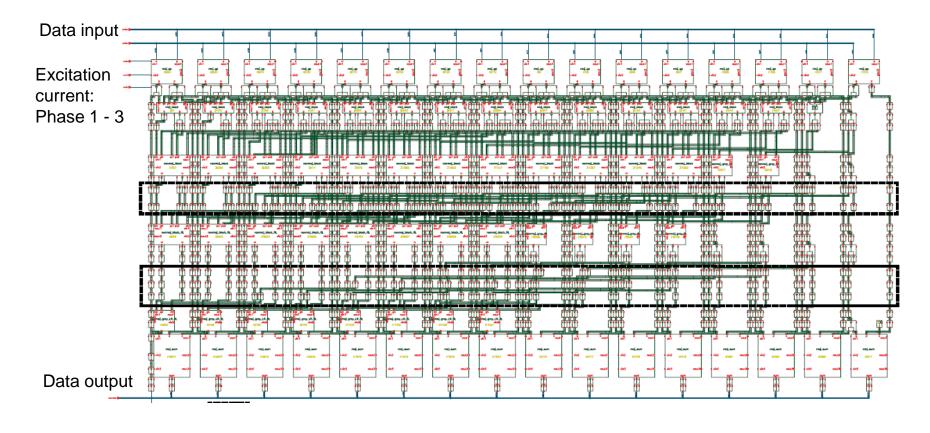

# Demonstrated 84k-Junction AQFP buffer array

#### AQFP is robust because

- The operation is based on differential pairs of junctions and inductances.

- The critical current of all junctions is the same.

| Area                | $6.68 \times 6.23 \text{ mm}^2$ |  |  |

|---------------------|---------------------------------|--|--|

| <b>Bias Current</b> | 3.60 mA                         |  |  |

| JJ number           | 83736                           |  |  |

YNU YOKOHAMA National University

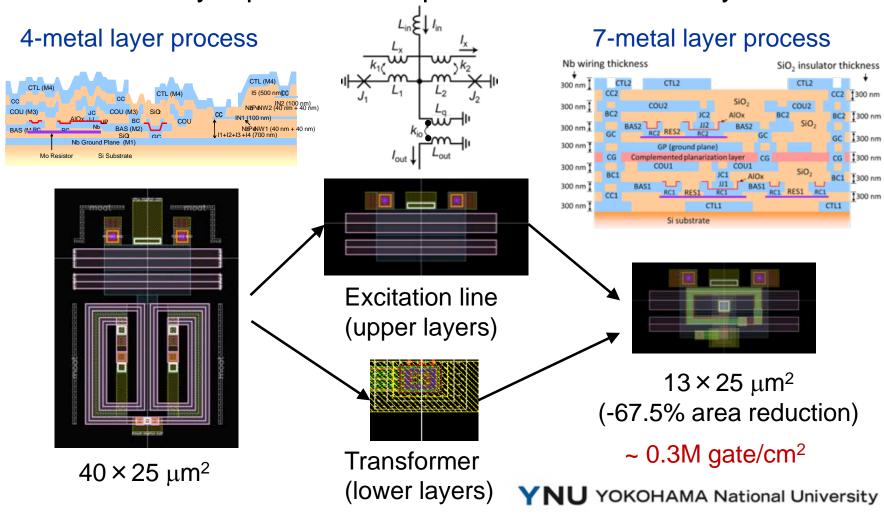

# **Density**

Multi-layer processes improve the circuit density.

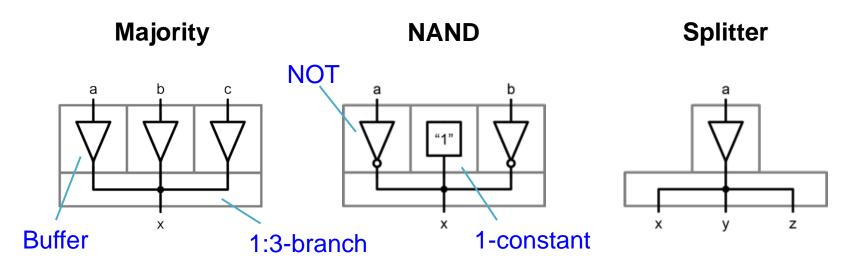

# **Design Methodology**

Logic cells can be designed by placing four building blocks:

Buffer, NOT, Constant, Branch

$$x = \text{MAJ}(a, b, c)$$

$$= a \cdot b + b \cdot c + c \cdot a$$

$$= \overline{ab}$$

$$x = \text{MAJ}(\overline{a}, 1, \overline{b})$$

$$= \overline{a} + \overline{b}$$

$$= \overline{ab}$$

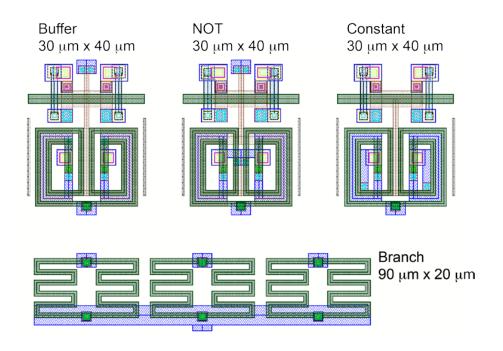

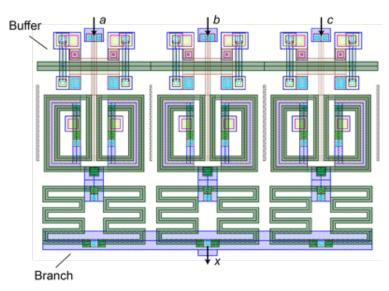

# **Layout of Basic Cells**

Symmetric design prevents the parasitic coupling between the excitation and output inductance.

#### **Building block cells**

#### **Majority cell**

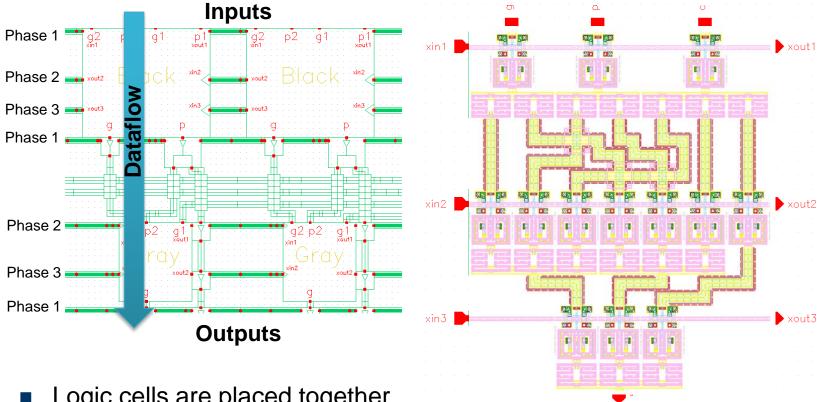

# **AQFP Logic Design**

- Logic cells are placed together like Lego blocks

- Logic gates grouped by phase & data flow

### **Demonstrated AQFP Circuits**

#### 16-word by 1-bit register file

#### 8-bit carry look-ahead adder

C. L. Ayala et al., IEEE Trans. Appl. Supercond., 27 (2017).

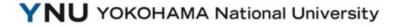

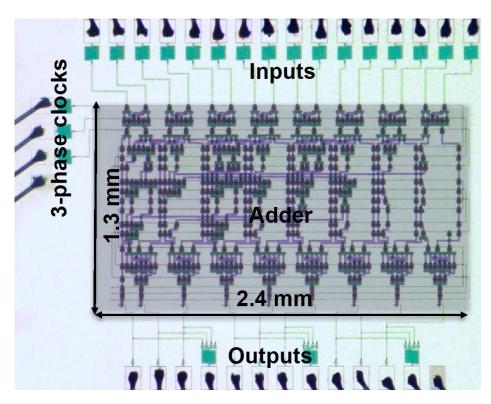

### 4-bit AQFP RISC Microarchitecture

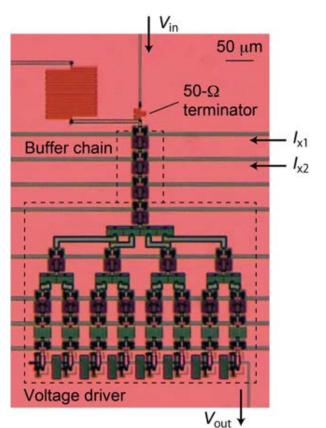

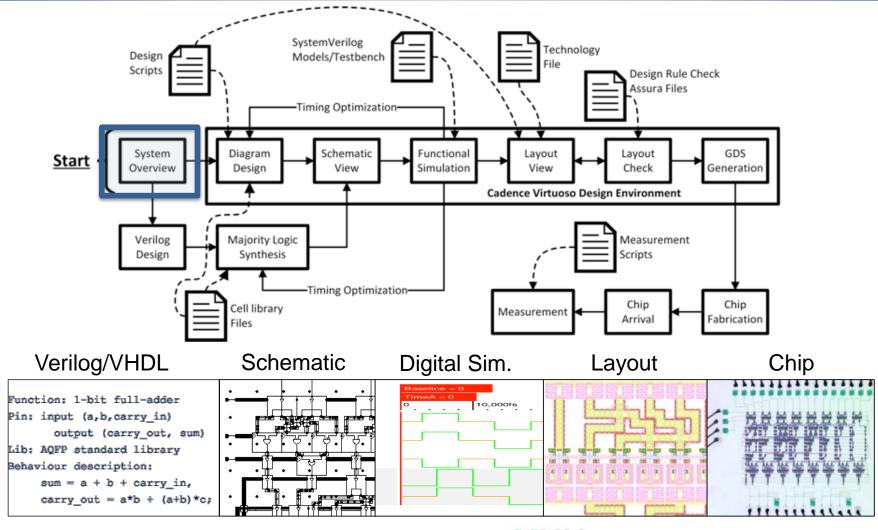

# **EDA Tools for Top-Down Design**

# **AQFP Circuit Design using EDA Tools**

#### Layout of 16-b AQFP carry-look-ahead adder

#### **Future Directions**

- Investigation of design methodology and EDA tools for large-scale AQFP integrated circuits

- Wire-length limitation

- Multi-phase clock distribution

- Majority-based logic synthesis

- Microprocessor architecture

- More energy efficient logic

- Use reversible QFP (RQFP) [1].

- New applications

- Control and readout circuits for Quantum computers

- Read out circuits for superconducting sensor arrays

# **Summary**

- Adiabatic quantum flux parametron (AQFP) is extremely energy efficient logic.

- ~1 zJ/bit @5 GHz

- Three orders of magnitude smaller than energy-efficient SFQ logic

- Six orders of magnitude smaller than CMOS logic

- AQFP has excellent properties as a logic circuit in terms of gain, functionality, speed, energy consumption, driving ability, error rates, robustness, and density.

- AQFP microprocessors are under development based on CMOS-like design methodology and top-down EDA tools.